Dual Channel Wide Band Not Reading the Same

In the fields of digital electronics and reckoner hardware, multi-channel memory architecture is a technology that increases the data transfer rate betwixt the DRAM memory and the retentiveness controller by adding more than channels of communication betwixt them. Theoretically, this multiplies the data charge per unit past exactly the number of channels present. Dual-channel retention employs two channels. The technique goes back as far as the 1960s having been used in IBM System/360 Model 91 and in CDC 6600.[1]

Modern high-end desktop and workstation processors as the AMD Ryzen Threadripper series and the Intel Core i9 Extreme Edition lineup support quad-channel memory. Server processors from the AMD Epyc series and the Intel Xeon platforms give back up to memory bandwidth starting from quad-aqueduct module layout to up to octa-channel layout.[2] In March 2010, AMD released Socket G34 and Magny-Cours Opteron 6100 series[three] processors with support for quad-channel retention. In 2006, Intel released chipsets that support quad-channel retentiveness for its LGA771 platform[4] and later in 2011 for its LGA2011 platform.[5] Microcomputer chipsets with fifty-fifty more than channels were designed; for example, the chipset in the AlphaStation 600 (1995) supports viii-channel memory, but the backplane of the machine limited operation to four channels.[6]

Dual-channel compages [edit]

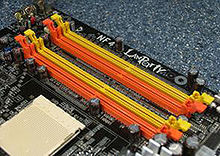

Dual-aqueduct memory slots, color-coded orangish and yellowish for this particular motherboard.

Dual-aqueduct-enabled memory controllers in a PC arrangement architecture utilize two 64-bit data channels. Dual-channel should not be confused with double data rate (DDR), in which data exchange happens twice per DRAM clock. The two technologies are independent of each other, and many motherboards apply both by using DDR memory in a dual-channel configuration.

Operation [edit]

Dual-aqueduct architecture requires a dual-aqueduct-capable motherboard and two or more DDR, DDR2, DDR3, DDR4, or DDR5 memory modules. The memory modules are installed into matching banks, each of which belongs to a different channel. The motherboard's manual will provide an explanation of how to install retentiveness for that particular unit. A matched pair of memory modules may ordinarily be placed in the first bank of each channel, and a unlike-capacity pair of modules in the second banking company.[vii] Modules rated at dissimilar speeds can exist run in dual-aqueduct mode, although the motherboard will so run all memory modules at the speed of the slowest module. Some motherboards, all the same, have compatibility bug with certain brands or models of memory when attempting to use them in dual-aqueduct mode. For this reason, information technology is generally brash to apply identical pairs of retentiveness modules, which is why well-nigh memory manufacturers now sell "kits" of matched-pair DIMMs. Several motherboard manufacturers only support configurations where a "matched pair" of modules are used. A matching pair needs to lucifer in:

- Chapters (east.one thousand. 1024 MB). Certain Intel chipsets support unlike chapters fries in what they phone call Flex Mode: the capacity that can be matched is run in dual-aqueduct, while the remainder runs in single-channel.

- Speed (e.g. PC5300). If speed is non the same, the lower speed of the two modules volition exist used. Also, the higher latency of the two modules will be used.

- Same CAS Latency (CL) or Column Address Strobe.

- Number of chips and sides (e.g. two sides with four chips on each side).

- Matching size of rows and columns.

Dual-channel architecture is a technology implemented on motherboards past the motherboard manufacturer and does not utilize to memory modules. Theoretically whatever matched pair of memory modules may be used in either single- or dual-aqueduct performance, provided the motherboard supports this architecture.

Performance [edit]

Theoretically, dual-channel configurations double the retentiveness bandwidth when compared to single-channel configurations. This should not be confused with double information charge per unit (DDR) retention, which doubles the usage of DRAM bus by transferring data both on the rising and falling edges of the retentiveness bus clock signals.

A benchmark performed by TweakTown, using SiSoftware Sandra, measured around 70% increment in operation of a quadruple-channel configuration, when compared to a dual-channel configuration.[8] : p. 5 Other tests performed past TweakTown on the same discipline showed no significant differences in performance, leading to a decision that non all benchmark software is up to the job of exploiting increased parallelism offered by the multi-channel retentivity configurations.[8] : p. 6

Ganged versus unganged [edit]

Dual-channel was originally conceived equally a way to maximize retentiveness throughput past combining two 64-bit buses into a single 128-bit bus.[ disputed ] [ commendation needed ] This is retrospectively chosen the "ganged" mode. All the same, due to lackluster performance gains in consumer applications,[9] more modern implementations of dual-aqueduct utilise the "unganged" fashion by default, which maintains two 64-bit memory buses but allows independent access to each channel, in back up of multithreading with multi-core processors.[x] [11]

"Ganged" versus "unganged" difference could also be envisioned every bit an analogy with the mode RAID 0 works, when compared to JBOD.[12] With RAID 0 (which is analogous to "ganged" mode), information technology is up to the boosted logic layer to provide amend (ideally fifty-fifty) usage of all available hardware units (storage devices, or retention modules) and increased overall performance. On the other manus, with JBOD (which is analogous to "unganged" style) it is relied on the statistical usage patterns to ensure increased overall performance through fifty-fifty usage of all available hardware units.[10] [11]

Triple-channel compages [edit]

Functioning [edit]

DDR3 triple-channel architecture is used in the Intel Core i7-900 serial (the Intel Core i7-800 series only support up to dual-channel). The LGA 1366 platform (e.g. Intel X58) supports DDR3 triple-aqueduct, unremarkably 1333 and 1600Mhz, but can run at higher clock speeds on sure motherboards. AMD Socket AM3 processors do not employ the DDR3 triple-channel architecture but instead use dual-aqueduct DDR3 memory. The same applies to the Intel Core i3, Cadre i5 and Core i7-800 series, which are used on the LGA 1156 platforms (east.g., Intel P55). According to Intel, a Core i7 with DDR3 operating at 1066 MHz will offering height data transfer rates of 25.six GB/s when operating in triple-aqueduct interleaved mode. This, Intel claims, leads to faster organization performance too every bit higher performance per watt.[13]

When operating in triple-channel mode, memory latency is reduced due to interleaving, meaning that each module is accessed sequentially for smaller bits of data rather than completely filling upward one module earlier accessing the next one. Data is spread amongst the modules in an alternating pattern, potentially tripling available memory bandwidth for the aforementioned amount of information, as opposed to storing it all on one module.

The architecture can but exist used when all three, or a multiple of 3, memory modules are identical in chapters and speed, and are placed in three-aqueduct slots. When two retentivity modules are installed, the architecture will operate in dual-channel architecture mode.[14]

Supporting processors [edit]

| Intel Cadre i7:

| Intel Xeon:

|

Quad-aqueduct architecture [edit]

Operation [edit]

Quad-channel DDR4 replaced DDR3 on the Intel X99 LGA 2011 platform, and is likewise used in AMD's Threadripper platform.[17] DDR3 quad-channel compages is used in the AMD G34 platform and in the Intel X79 LGA 2011 platform. AMD processors for the C32 platform and Intel processors for the LGA 1155 platform (e.m. Intel Z68) utilise dual-channel DDR3 memory instead.

The architecture tin can be used merely when all four retention modules (or a multiple of four) are identical in chapters and speed, and are placed in quad-aqueduct slots. When two retentivity modules are installed, the architecture volition operate in a dual-channel mode; When three memory modules are installed, the compages volition operate in a triple-channel mode.[14]

Supporting processors [edit]

| AMD Threadripper:

| Intel Core:

| Intel Xeon:

|

Hexa-aqueduct architecture [edit]

Supported by Qualcomm Centriq server processors,[20] and processors from the Intel Xeon Scalable platform.[21]

Octa-channel architecture [edit]

Supported by Cavium ThunderX2 server processors, AMD'south server processors from their Epyc platform, and the Threadripper PRO lineup of professional-class workstation processors from AMD Ryzen PRO product family.[22] [23] [24]

Run into also [edit]

- List of device bandwidths

- Lockstep (computing)

References [edit]

- ^ Jacob, Bruce; Ng, Spencer; Wang, David (2007). Memory systems: cache, DRAM, disk. Morgan Kaufmann. p. 318. ISBN978-0-12-379751-iii.

- ^ jpringle (September 12, 2017). "Benchmarking Epyc, Ryzen, and Xeon: Tyranny of Memory". Regional Ocean Modeling System . Retrieved April 23, 2021.

{{cite web}}: CS1 maint: url-status (link) - ^ a b "Opteron 6000 Series Platform Quick Reference Guide" (PDF). AMD. Archived from the original (PDF) on 2012-05-12. Retrieved 2012-x-15 .

- ^ 5000P memory controller, Intel .

- ^ Intel LGA2011 socket x68 express chipset pictured, Tech power up .

- ^ John H. Zurawski; John Eastward. Murray; Paul J. Lemmon, "The Pattern and Verification of the AlphaStation 600 five-series Workstation", HP, 7 (i) .

- ^ "Intel Dual-Aqueduct DDR Memory Architecture White Paper" (PDF) (Rev. ane.0 ed.). Infineon Technologies North America and Kingston Technology. September 2003. Archived from the original (PDF, 1021 KB) on 2011-09-29. Retrieved 2007-09-06 .

- ^ a b Shawn Baker (2011-xi-16). "Intel X79 Quad Channel and Z68 Dual Channel Memory Performance Assay". TweakTown. Retrieved 2013-11-30 .

- ^ "AMD Phenom X4 Retentivity Controller in the Ganged/ Unganged Manner". ixbtlabs.com. 2008-08-16. Retrieved 2014-01-09 .

- ^ a b Gionatan Danti (2010-06-17). "The Phenom / PhenomII retentiveness controller: ganged vs unganged mode benchmarked". ilsistemista.net . Retrieved 2014-01-09 .

- ^ a b "BIOS and Kernel Programmer'southward Guide (BKDG) For AMD Family unit 10h Processors" (PDF). amd.com. 2013-01-11. pp. 107–108. Retrieved 2014-01-09 .

When the DCTs are in ganged mode, every bit specified past [The DRAM Controller Select Low Register] F2x110 [DctGangEn], then each logical DIMM is two channels broad. Each concrete DIMM of a 2-channel logical DIMM is required to be the same size and use the same timing parameters. Both DCTs must be programmed with the same data (see ii.eight.one [DCT Configuration Registers]). When the DCTs are in unganged mode, a logical DIMM is equivalent to a 64-chip physical DIMM and each channel is controlled by a dissimilar DCT. Typical systems are recommended to run in unganged mode to do good from the additional parallelism generated past using the DCTs independently. See ii.12.two [DRAM Considerations for ECC] for DRAM ECC implications of ganged and unganged mode. Ganged style is not supported for S1g3, S1g4, ASB2, and G34 processors.

- ^ Rouse, Margaret (September 2005). "JBOD (only a bunch of disks or simply a agglomeration of drives)". SearchStorage.TechTarget.com . Retrieved 2014-01-09 .

- ^ X58 Product Brief (PDF), Intel

- ^ a b Desktop Boards – Triple Memory Modules, Intel , Single- and Multichannel Memory Modes

- ^ "Cadre i7 Family Product Comparison". Intel. Memory Specifications: # of Memory Channels.

- ^ "Xeon Family unit Product Comparing". Intel. Memory Specifications: # of Retention Channels.

- ^ AMD Ryzen Threadripper And Vega Attack Casualty At 4K, Quad GPUs Shred Blender, Radeon RX Vega Hits In July, "....with 16 cores and 32 threads with support for quad-aqueduct DDR4 retentivity......"

- ^ "AMD Opteron 6300 Series processor Quick Reference Guide" (PDF) . Retrieved 2013-12-11 .

- ^ "AMD Opteron 6200 Series Processor Quick Reference Guide" (PDF) . Retrieved 2012-x-15 .

- ^ Kennedy, Patrick (23 August 2017). "Qualcomm Centriq 2400 ARM CPU from Hot Fries 29". Serve The Domicile. Retrieved 14 Nov 2017.

- ^ "Intel® Xeon® Statuary 3106 Processor (11M Cache, 1.70 GHz)". www.intel.in.

- ^ Cutress, Ian (7 March 2017). "AMD Prepares 32-Core Naples CPUs for 1P and 2P Servers: Coming in Q2". Anandtech. Retrieved 7 March 2017.

- ^ Kennedy, Patrick (9 November 2017). "Cavium ThunderX2 and OCP Platform Details". Serve the Domicile. Retrieved xiv November 2017.

- ^ Cutress, Ian (July xiv, 2021). "AMD Threadripper Pro Review: An Upgrade Over Regular Threadripper?". AnandTech . Retrieved Baronial xviii, 2021.

{{cite web}}: CS1 maint: url-status (link)

External links [edit]

- "Unmarried, dual, triple and flex memory modes", Desktop motherboards support, Intel .

- Everything You lot Demand to Know About the Dual-, Triple-, and Quad-Channel Retentivity Architectures, November 2011, Hardware Secrets

- Memory Configuration Guide for X9 Series DP Motherboards – Revised Ivy Span Update (Socket R & B2), Jan 2014, Super Micro Computer, Inc.

- DDR3 Memory Frequency Guide, May 2012, AMD (archived)

Source: https://en.wikipedia.org/wiki/Multi-channel_memory_architecture

0 Response to "Dual Channel Wide Band Not Reading the Same"

Postar um comentário